# A Variable Power Factor High Power Testbed for Traction Inverter Using Back-to-Back Connection

Yukun Luo FREEDM Systems Center North Carolina State University yluo9@ncsu.edu

Wensong Yu FREEDM Systems Center North Carolina State University wyu2@ncsu.edu Li Yang FREEDM Systems Center North Carolina State University lyang20@ncsu.edu Juhamatti Korhonen Laboratory of Applied Electronics Lappeenranta University of Technology Juhamatti.Korhonen@lut.fi

Iqbal Husain FREEDM Systems Center North Carolina State University ihusain2@ncsu.edu

Abstract—A new inverter test method using back-to-back inverter power circulating strategy is presented in this paper. Using the method, high power test for traction inverter with wide power factor range can be achieved by selecting appropriate modulation scheme. The zero-sequence current issue inherent to the setup is investigated and addressed in order to improve the output current quality. Moreover, the similarities and the differences between the proposed setup and open-end winding motor drives are discussed. Experimental results verifying the high-power operation with wide power factor range achievable by the proposed method are provided.

Index Terms—Traction Drive, Back-to-Back, Inverter test, Power Factor

# I. INTRODUCTION

The power rating of Electrical Vehicle (EV) traction drive can range from 30 kW to 250 kW [8-13], and the testing of these traction inverters with conventional R-L load are difficult and expensive. On the one hand, high rating power supply and load bank are needed for the entire operation range. While on the other hand, achieving tests with wide range of power factor requires good match between the inductor/resistor values and the fundamental frequency. Because of the limitations, many circulating test strategies have been used in practice. In [1,2], motor and generator emulator concept are proposed for the same inverter back-to-back setup as proposed in this paper achieving variable load conditions but only at a low power level and additional communication is needed. In [14,15], similar testing with circulating power have been implemented at an increased power level, but additional hardware, like dynamo-meter and transformers, are required. The circulating power test setup could also be used as a power system emulator as presented in [16]. In this paper, a testing method using similar topology as open-end-winding motor drive is used for circulating high power test on the traction inverter with high power flow control accuracy and full power factor range adjust ability. In the proposed method, no load bank is needed, and only a small DC power source to supply the system loss is required. With the modulation and control strategy proposed in the paper, high power level and full range (0 to

1) adjustable power factor can be achieved for the inverter under test simultaneously. The main contribution of this paper is the derivation and visualization of the relationship between achieved power factor and modulation parameters.

# II. TOPOLOGY AND OPERATION PRINCIPLE

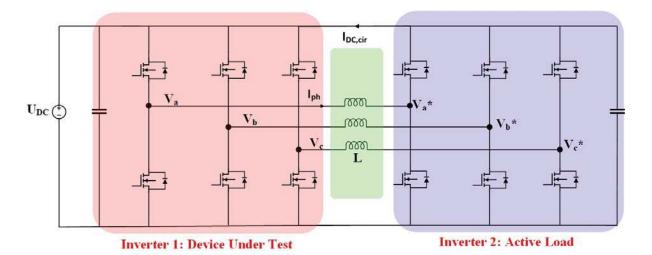

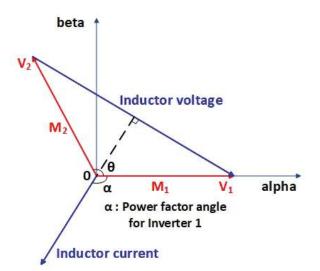

The testing system consists of two back-to-back inverters with inductor load connected in between, as shown in Fig. 1. The basic idea is to adjust the voltage vectors of the two backto-back connected inverters so that magnitude and phase angle of the voltage across inductor loads can be changed. In this way, the output power of Inverter 1 and power factor angle can be controlled. The concept is shown in Fig. 2, where V<sub>1</sub> and V<sub>2</sub> are the two voltage vectors modulated for Inverter 1 and Inverter 2 with magnitude of M<sub>1</sub> and M<sub>2</sub> and phase shift of  $\theta$ . The voltage across inductor load will be the vector difference between V<sub>1</sub> and V<sub>2</sub>. The inductor current orthogonal to inductor voltage will be away from V<sub>1</sub> by angle  $\alpha$ , which to Inverter 1 is a load with cos ( $\theta$ ) power factor. Based on the strategy, the target apparent power output from Inverter 1 S<sub>INV1</sub> can be calculated as:

$$S_{INV1} = \frac{3}{2} \cdot M_1 \cdot \left(\frac{U_{DC}}{2}\right)^2 \cdot \frac{\sqrt{M_1^2 + M_2^2 - 2 \cdot M_1 \cdot M_2 \cdot \cos(\theta)}}{2\pi f \cdot L}$$

(1)

The power factor under given modulation index  $M_1/M_2$  and phase angle  $\theta$  is:

$$PF = -\sin\left(\arctan\left(\frac{\sin\left(\theta\right)}{\frac{M_{1}}{M_{2}} - \cos\left(\theta\right)}\right)\right)$$

(2)

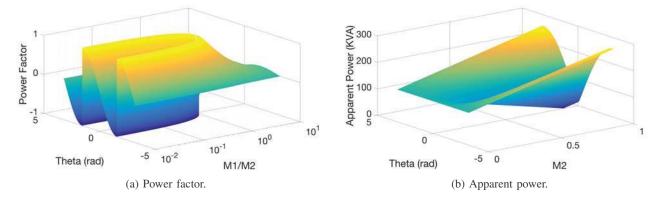

A 3D graph of power factor with respect to modulation index ratio  $M_1/M_2$  and phase shift angle  $\theta$  is plotted in Fig. 3(a) based on (2). The range of  $M_1/M_2$  is chosen within range from 0 to 10, and phase shift angle  $\theta$  is within  $-\pi$  to  $\pi$ . From the plotted figure, it can be seen that a wide power factor range is achievable. Based on (1), if  $M_1$  is kept at 0.9, a 3D graph of apparent power (S) with respect to  $M_2$  and phase shift angle Theta can also be plotted, as shown in Fig. 3(b) where  $U_{DC} =$ 600 V, fundamental frequency f = 95 Hz and load inductance is

978-1-4799-7312-5/18/\$31.00 ©2018 IEEE

Fig. 1: Back-to-back inverter circulating test setup.

1.5 mH per phase. For practical implementation, phase current could be limited below system maximum value according to (3), the feasible operating region is then determined. Thus, by choosing proper modulation indexes and phase shift angle  $\theta$  for the two inverters, the setup could be operated with a wide range of power factor and high output power level.

$$\left(\frac{U_{DC}}{2}\right)^2 \cdot \frac{\sqrt{M_1^2 + M_2^2 - 2 \cdot M_1 \cdot M_2 \cdot \cos(\theta)}}{2\pi f \cdot L} \leq I_{\max} \qquad (3)$$

# **III. ZSC SOURCE AND SUPPRESSION**

### A. Modulation Strategy

The main reason that sinusoidal PWM (SPWM), instead of space vector PWM (SVPWM), is chosen for this test setup is that SVPWM strategy would introduce huge zerosequence current. The zero-sequence current (ZSC) issue is

Fig. 2: Vector diagram.

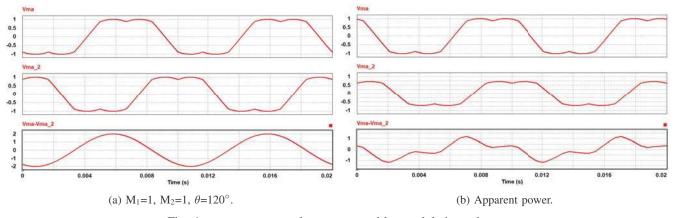

inherent to parallel three-phase inverters sharing only one DC power supply. As mentioned in previous works [3-5], the main source of ZSC are asynchronous carrier, zero sequence voltage introduced by PWM modulation and dead-band time. This issue has already been observed and discussed for open-end winding motor drive [3, 4, 6]. For open-end winding motor drive with SVPWM modulation, the reference voltages are modulated 120° phase shifted with the same magnitude in order to eliminate the zero-sequence voltage. However, for the testing purpose as in this paper, in order to change the power factor and power level of the inverters, the phase angle shift and modulation indexes need to be freely changed, which then generates zero sequence voltage. The effect is simulated in PSIM as shown in Fig. 4, where  $V_{ma}$  and  $V_{ma2}$  are the two reference voltages of the same phase leg for Inverter 1 and Inverter 2, while  $V_{ma}$ - $V_{ma2}$  is the voltage applied across the inductor load. Fig. 4(a) shows the case where the two references have same magnitudes and 120° phase shift, while Fig. 4(b) shows the case where the two references have different magnitudes and phase shift of 45°. It can be seen that the inductor voltage will be sinusoidal for case (a). But inductor voltage will contain zero sequence components in case (b). Meaning only under the condition of same modulation index and 120° phase shift will two SVPWM modulated back-toback inverters generate pure sinusoidal current in the load. According to [7], the harmonic injected in SVPWM is given by (4), which verifies that the harmonics could only be canceled if the phase angle shift is 120° and their modulation indexes are the same, otherwise there is zero sequence voltage applied on the load inductors, as illustrated in Fig. 4. Because of aforementioned limitations on SVPWM, SPWM is used in this application.

Fig. 3: 3D plot of power factor and apparent power versus modulation indexes and phase shift angle.

Fig. 4: zero sequence voltage generated by modulation scheme.

$$V_{ma} = MI \cdot \left[ \sin(\omega t + \theta) + 0.25 \\ \cdot \left( \sum_{i=0}^{N} (-1)^n \cdot n^{-2} \cdot \sin(3n(\omega t + \theta)) \right) \right]$$

(4)

$$(n = 2i + 1)$$

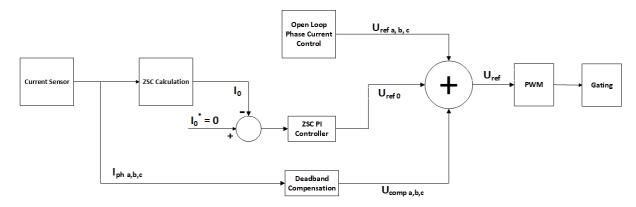

# B. Deadband Time Effect

Incorporation of dead-band time into the inverter operation is another source of zero sequence current. In this paper, dead-band time compensation and zero-sequence PI controller [6] are both used. In order to have minimal modification on the device under test (Inverter 1), all the deadband time compensation and control algorithm are only applied to active load (Inverter 2). Therefore the device under test (Inverter 1) only has the simple open loop phase current control. In [3], the effect of dead-band time on zero-sequence voltage has been investigated. From switching cycle point of view, during dead-band time the current commutates through the body diode causing zero-sequence voltage. The average zerosequence voltage over one switching period can be written as (5). Where  $t_D$  is the dead-band time,  $T_{sw}$  the switching period, and  $U_{DC}$  the DC link voltage. From fundamental cycle point of view, the polarity of zero-sequence voltage changes every 60° (fundamental frequency) as one of the three-phase load current changes polarity. The dead-band time compensation modifies each phases voltage reference based on each phases current polarity [5], the details are shown in Table I. The overall zero-sequence current control block diagram for Inverter 2 is shown in Fig. 5.

$$U_0 = \frac{2 \cdot t_D \cdot U_{DC}}{3 \cdot T_{sw}} \tag{5}$$

# C. Carrier Synchronization

In the setup, two inverters are controlled by two individual DSPs, it is crucial to synchronize their carrier wave. Asynchronous carrier wave of the two controllers is the third source of ZSC. In order to eliminate the effect of asynchronous

# TABLE I: Deadband Time Compensation Value

| DB Comp Value           | $I_n < 0 (n = a,b,c)$            | $I_n \ge 0 (n = a,b,c)$ |

|-------------------------|----------------------------------|-------------------------|

| U <sub>comp a,b,c</sub> | -t <sub>D</sub> /T <sub>sw</sub> | $t_D/T_{sw}$            |

Fig. 5: ZSC suppression block diagram for Inverter 2.

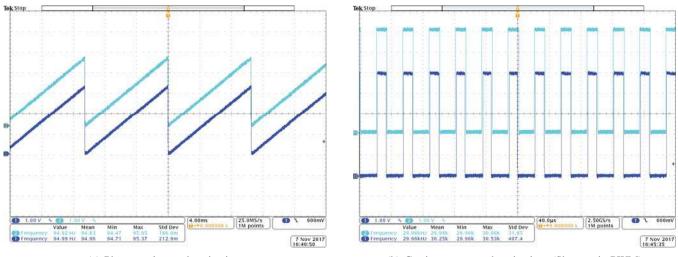

carrier, external synchronization has to be adopted. From practical implementation point of view, phase angle of both voltage vectors  $(V_1 \text{ and } V_2)$  modulated for each inverter has also to be synchronized. Because asynchronous phase angle of voltage vector  $V_1$  and  $V_2$  would result in unstable phase shift angle  $\theta$ . If the carriers are aligned with each other, current ripple on the DC link as well as sinusoidal phase current output can be minimized [17]. In the previous works [1,2], the carrier synchronization and phase angle synchronization are realized via CAN communication and PLL respectively. In this work, however, two inverters are synchronized using one common external pulse signal of fundamental frequency. And a synchronization board is connected to both inverters with optical fiber cable. The function of the synchronization board is to generate and transmit the synchronization pulse at the fundamental frequency of sine waves. For the phase angle synchronization, two controller DSPs execute their phase angles incremental with the same frequency, and when the external pulse is detected, both DSP reset their phase angle to zero. Thus, the phase angle is synchronized once every

fundamental cycle. As for the carrier wave, the external pulse signal is connected to the synchronization inputs of EPWM module of both DSPs such that whenever there is pulse coming from the synchronization board, the carriers of the two DSPs are reset by hardware. The synchronized phase angle and PWM carrier wave are shown in Fig. 6(a) and Fig. 6(b) respectively.

### IV. EXPERIMENTAL RESULTS

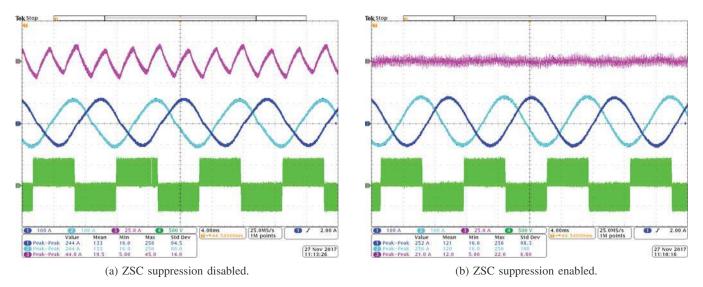

# A. ZSC Suppression

To verify the proposed inverter testing method, a setup consists of two high power inverters utilizing SiC devices with liquid cooling is built. The testing parameters are listed in Table. II. The overall ZSC suppression strategy block diagram is shown in Fig. 5. The effectiveness of ZSC suppression strategies is verified via experiment first. In this test, the modulation indexes of Inverter 1 and Inverter 2 are kept at 0.2 and the phase shift angle  $\theta$  is set to be 120°. The results are shown in Fig. 7(a) and Fig. 7(b) respectively with ZSC suppression disabled and enabled. From the experimental

(a) Phase angle synchronization.

(b) Carrier wave synchronization. (Shown via PWM)

Fig. 6: Synchronization verification.

Fig. 7: ZSC suppression result. CH1, CH2: phase current, CH3: ZSC (x3), CH4: phase to phase voltage (Vab) of Inverter 1.

results, the third harmonic in ZSC is significantly reduced and the peak-to-peak value of three phase current summation (*i.e.*, three times the ZSC) is reduced from 44 A to 21 A. Evident to see that with the ZSC suppression algorithm, the quality of sinusoidal phase current gets improved significantly.

TABLE II: Back-to-back Inverter Test Setup Parameters

| Parameters                                             | Value  |

|--------------------------------------------------------|--------|

| DC Link Voltage $(U_{DC})$                             | 600 V  |

| Switching Frequency $(1/T_{sw})$                       | 30 kHz |

| Fundamental Frequency (f)                              | 95 Hz  |

| Load Inductance (L)                                    | 1.5 mH |

| Phase Current Limit (Imax)                             | 130 A  |

| Dead-band Time $(t_D)$                                 | 600 ns |

| Inverter 2 ZSC PI controller proportional term $(K_P)$ | 4.8    |

| Inverter 2 ZSC PI controller integral term $(K_I)$     | 0.048  |

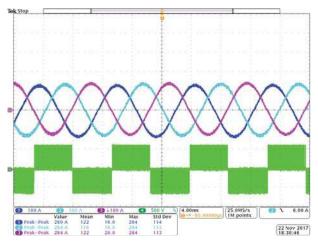

(a) Three-phase current and phase-to-phase voltage  $V_{ab}$ .

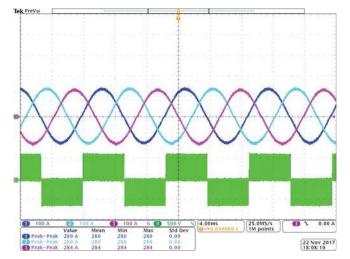

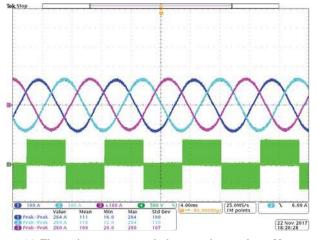

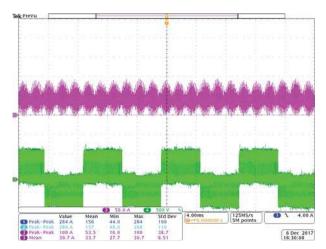

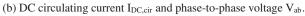

#### B. Variable Power Factor Operation

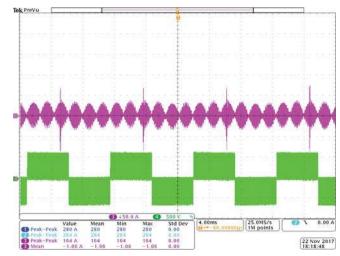

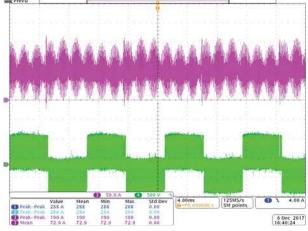

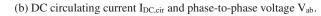

In order to verify the proposed variable power factor testing method, experiments were designed as follow. The maximum system apparent power and maximum phase current amplitude are set as 45 kVA and 130 A respectively, considering the actual test setup parameters and ratings. Then four theoretical power factor operation points 0, 0.5, 0.866 and 1 are selected. Based on the constraints above, the combination of modulation indexes  $M_1$ ,  $M_2$  and angle  $\theta$  could be calculated according to (1)-(3), shown in Table. III. In this way, all the setting parameters under various power factor operation could be obtained. The relation between achieved apparent power of Inverter 1 S<sub>INV1</sub> and modulation index  $M_1$  is described in (6). And by measuring the DC circulating current I<sub>DC,cir</sub> (labeled in Fig. 1), the real power circulating within the system can be

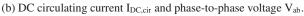

(b) DC circulating current  $I_{DC,cir}$  and phase-to-phase voltage  $V_{ab}$ .

Fig. 8: PF = 0.

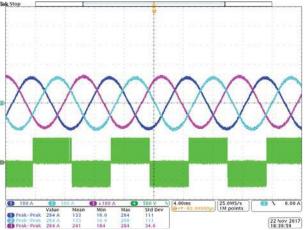

(a) Three-phase current and phase-to-phase voltage  $V_{ab}. \label{eq:value}$

Fig. 9: PF = 0.5.

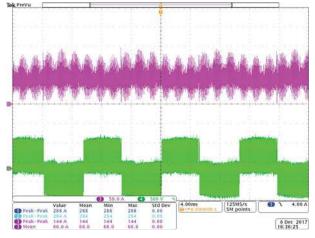

(a) Three-phase current and phase-to-phase voltage  $V_{ab}. \label{eq:vab}$

(a) Three-phase current and phase-to-phase voltage V<sub>ab</sub>.

Fig. 10: PF = 0.866.

Fig. 11: PF = 1.

.00 A

TABLE III: Comparison between theoretical calculation and experimental results

| Target PF | Target S <sub>INV1</sub> | M <sub>1</sub> | M <sub>2</sub> | θ       | Actual S <sub>INV1</sub> | I <sub>ph</sub> | I <sub>DC,cir</sub> | P <sub>cir</sub> | Ploss   | Actual PF |

|-----------|--------------------------|----------------|----------------|---------|--------------------------|-----------------|---------------------|------------------|---------|-----------|

| 0         | 45 kVA                   | 0.7692         | 0.3813         | 0°      | 45.00 kVA                | 130 A           | 1.1 A               | 0.66 kW          | 3.00 kW | 0.048     |

| 0.5       | 45 kVA                   | 0.7692         | 0.4747         | 24.122° | 45.00 kVA                | 130 A           | 39.7 A              | 23.82 kW         | 3.00 kW | 0.563     |

| 0.866     | 45 kVA                   | 0.7692         | 0.6662         | 30.288° | 45.34 kVA                | 131 A           | 66.0 A              | 39.60 kW         | 3.06 kW | 0.907     |

| 1         | 45 kVA                   | 0.7692         | 0.8615         | 26.765° | 45.69 kVA                | 132 A           | 72.9 A              | 43.74 kW         | 3.12 kW | 0.991     |

calculated according to (7).

$$\mathbf{S}_{INV1} = \frac{3}{2} \cdot \frac{U_{DC}}{2} \cdot M_1 \cdot I_{ph} \tag{6}$$

$$P_{cir} = U_{DC} \cdot I_{DC, cir} \tag{7}$$

Thus, the theoretical power factor could be verified against the experimental results. The experimental results for 0, 0.5, 0.866, and 1 power factor operation are shown from Fig. 8 to Fig. 11 respectively. It can be seen that the peak-to-peak ripple in phase current is around 20 A, which causes difference between current peak value and amplitude. From averaging point of view, during power calculation, the current amplitude should be used. The comparison of theoretical calculation and experimental results for these four cases is shown in Table. III. The actual power factor can be calculated according to (8). One can assume the power supplied by the DC source is equal to the sum of power loss over two inverters and load inductors. In this way, the power loss on Inverter 1 could be obtained. After analyzing the experimental results, there are several phenomenon worth noting. First, there is some slight DC offset within three-phase current shown in Fig. 8(a) to Fig. 11(a). Second, the phase current amplitude has small error with regard to reference value 130 A under 0.866 and 1 power factor operation scenarios. These two are due to the fact that open loop phase current control is utilized as shown in Fig. 5. A more accurate close loop phase current controller would mitigate the DC offset and static error. Also, the envelop of DC circulating current I<sub>DC,cir</sub> is three times the fundamental frequency. While the high frequency current ripple is introduced by the switching of the MOSFET. Moreover, higher real power require higher DC current ripple to circulate energy within the system. From Table. III, one can see that the theoretically calculated power factor is matching with the experimental results pretty closely. However, slight error do exist, which is mainly contributed by the parasitic resistance of the load inductors.

$$Actual PF = \frac{P_{cir} + 0.5P_{loss}}{\mathbf{S}_{INV1}} \tag{8}$$

### V. CONCLUSION AND FUTURE WORK

From the experimental results shown above, high power level variable power factor operation of the traction inverter can be achieved utilizing back-to-back topology, which eliminate the need for high capacity bidirectional power supply, huge load bank and dynamo-meter setup. Also, no additional communication protocol between two inverters is required to suppress the zero-sequence current, introduced by asynchronous phase angle and carrier wave of the controllers of the two inverters. Appropriate PWM scheme and dead-band time compensation are used to mitigate other sources of zerosequence current in the system. However, some DC offset between three phase current and static current error do exist. In the future, a variable power factor control scheme utilizing close loop current controller could be developed to address this issue.

#### REFERENCES

- L. Yang et al., "Hardware implementation and control design of generator emulator in multi-converter system," 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 2013, pp. 2316-2323.

- [2] J. Wang, Y. Ma, L. Yang, L. M. Tolbert and F. Wang, "Power converterbased three-phase induction motor load emulator," 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, 2013, pp. 3270-3274.

- [3] J. Korhonen, J. Honkanen, T. J. Krkkinen, J. Nerg and P. Silventoinen, "Modulation and control methods to reduce zero sequence current in open-end winding motors," 2017 IEEE International Electric Machines and Drives Conference (IEMDC), Miami, FL, 2017, pp. 1-6.

- [4] H. Zhan, Z. q. Zhu and M. Odavic, "Analysis and Suppression of Zero Sequence Circulating Current in Open Winding PMSM Drives with Common DC Bus," IEEE Transactions on Industry Applications, vol. 53, no. 4, pp. 3609-3620, July-Aug. 2017.

- [5] A. C. Oliveira, C. B. Jacobina and A. M. N. Lima, "Improved Dead-Time Compensation for Sinusoidal PWM Inverters Operating at High Switching Frequencies," IEEE Transactions on Industrial Electronics, vol. 54, no. 4, pp. 2295-2304, Aug. 2007.

- [6] Q. An, J. Liu, Z. Peng, L. Sun and L. Sun, "Dual-Space Vector Control of Open-End Winding Permanent Magnet Synchronous Motor Drive Fed by Dual Inverter," IEEE Transactions on Power Electronics, vol. 31, no. 12, pp. 8329-8342, Dec. 2016.

- [7] D. G. Holmes, "The significance of zero space vector placement for carrier-based PWM schemes," IEEE Transactions on Industry Applications, vol. 32, no. 5, pp. 1122-1129, Sep/Oct 1996.

- [8] A. Merkert, J. Mller and A. Mertens, "Component design and implementation of a 60 kW full SiC traction inverter with boost converter," 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, 2016, pp. 1-8.

- [9] S. Yano et al., "Development of compact power control unit for HEVs," 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 2017, pp. 584-588.

- [10] K. Olejniczak et al., "A compact 110 kVA, 140C ambient, 105C liquid cooled, all-SiC inverter for electric vehicle traction drives," 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, 2017, pp. 735-742.

- [11] D. Rahman et al., "Design methodology for a planarized high power density EV/HEV traction drive using SiC power modules," 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, 2016, pp. 1-7.

- [12] A. H. Wijenayake et al., "Design of a 250 kW, 1200 V SiC MOSFETbased three-phase inverter by considering a subsystem level design optimization approach," 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 2017, pp. 939-946.

- [13] M. Anwar, M. Teimor, P. Savagian, R. Saito and T. Matsuo, "Compact and high power inverter for the Cadillac CT6 rear wheel drive PHEV," 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, 2016, pp. 1-7.

[14] M. H. Hedayati and V. John, "Circulating power test setup for a PWM

- [14] M. H. Hedayati and V. John, "Circulating power test setup for a PWM rectifier motor drive," 2012 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Bengaluru, 2012, pp. 1-5.

- [15] Shyh-Jier Huang and Fu-Sheng Pai, "A new approach of circulating current method for UPS testing with energy recovery," IEEE Power Engineering Society Summer Meeting, Chicago, IL, USA, 2002, pp. 1418-1422 vol.3.

- [16] Y. Ma, L. Yang, J. Wang, F. Wang and L. M. Tolbert, "Emulating fullconverter wind turbine by a single converter in a multiple converter based emulation system," 2014 IEEE Applied Power Electronics Conference and Exposition - APEC 2014, Fort Worth, TX, 2014, pp. 3042-3047.

- [17] L.G. Gonzlez, G. Garcer, E. Figueres, R. Gonzlez, Effects of the PWM carrier signals synchronization on the DC-link current in back-to-back converters, In Applied Energy, Volume 87, Issue 8, 2010, Pages 2491-2499, ISSN 0306-2619.