# FREESTA SYSTEMS CENTER

### SiC JFETs for Circuit Protection

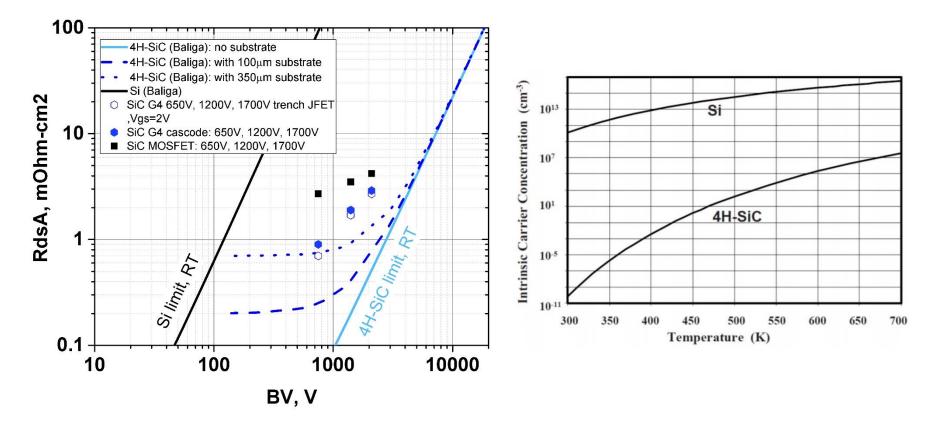

Why SiC?

Key properties

- Low RdsA for a given BV for unipolar devices, due to 10X higher E<sub>CRIT</sub>

- High peak operating temperatures

- 3X Higher thermal conductivity than Si

- Ability to handle 4X energy to failure than Si per unit area

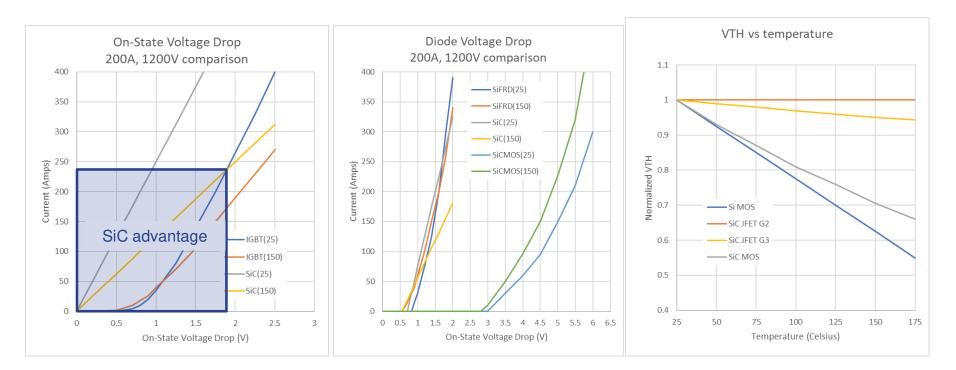

## SiC FET Advantages ≥ 1200V

Normally-on SiC JFETs offer lowest RdsA

SYSTEMS CENTER

- IGBTs great at high currents, but knee voltage leads to unwanted losses in most operating conditions

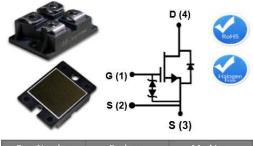

- Normally-off FET created using stack cascode, Si MOSFET on SiC JFET

- Si MOSFET adds Rds, but operates at a positive Vgs

- Excellent reverse conduction characteristic, similar to Si diode

- No gate oxide degradation issues

- Normally-on JFET Vth is insensitive to temperature more thermally stable

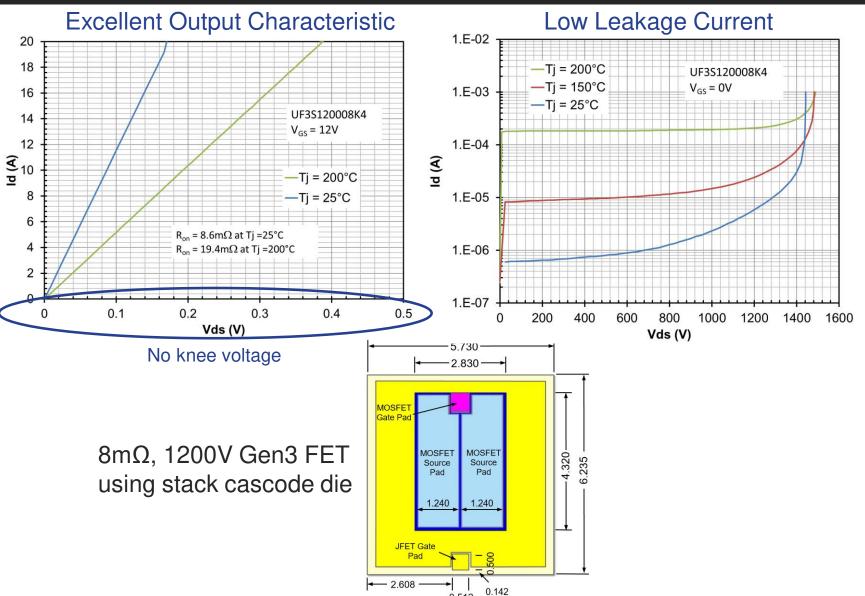

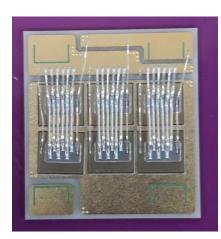

## 1200V SiC Stack Cascode Example

0.512

SYSTEMS CENTER

#### FREEDIN SYSTEMS CENTER

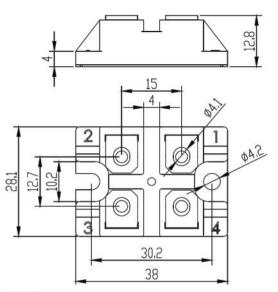

### $2m\Omega$ , 1200V SOT-227 SiC FET

Unit: mm

#### United SiC

#### xJ SiC Series | $1.8m\Omega$ - 1200V SiC Cascode | UF3SC120002SNS

Datasheet

#### Description

Features

United Silicon Carbide's cascode products co-package its highperformance F3 SiC fast JFETs with a cascode optimized MOSFET to produce the only standard gate drive SiC device in the market today. This device is ideally suited for circuit breaker, solid state switch and synchronous rectification applications, using a standard gate drive, and providing very high current capability in the familiar SOT227 footprint. The baseplateless construction with advanced internal packaging provides very low thermal impedence.

| Part Number    | Package | Marking        |  |  |

|----------------|---------|----------------|--|--|

| UF3SC120002SNS | SOT-227 | UF3SC120002SNS |  |  |

#### **Typical Applications**

- EV charging

- Synchronous rectifiers

- Solid state circuit breakers

- Solid state load switch

- Motor drives

- Induction heating

AIN for improved RthJC

SOT227 package for high current handling

Typical on-resistance  $R_{DS(on,typ}$  of  $1.8m\Omega$

Maximum operating temperature of 175°C

Standard 12V gate drive

**Excellent Reverse Recovery**

Low intrinsic capacitance

ESD protected, HBM class 2

Low gate charge

- Ag sinter interfaces

- Au plated bottom

- Package can be sintered to heat sink

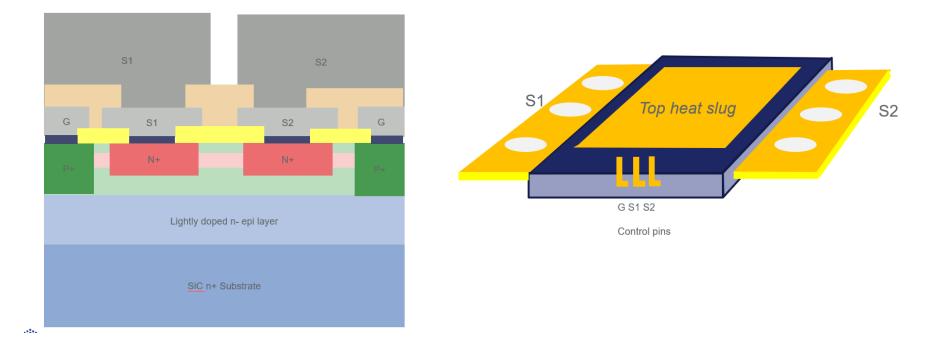

- For very low voltages and bidirectional circuit breakers, this lateral structure eliminates substrate resistance

- With state-of-the-art packaging, 1mΩ, 100V 3x6mm<sup>2</sup> chips can be paralleled to form high current breakers with resistances < 0.1mΩ</li>

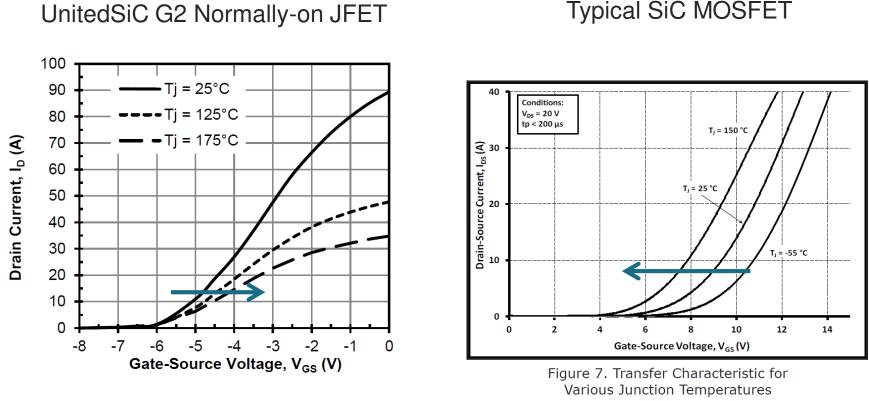

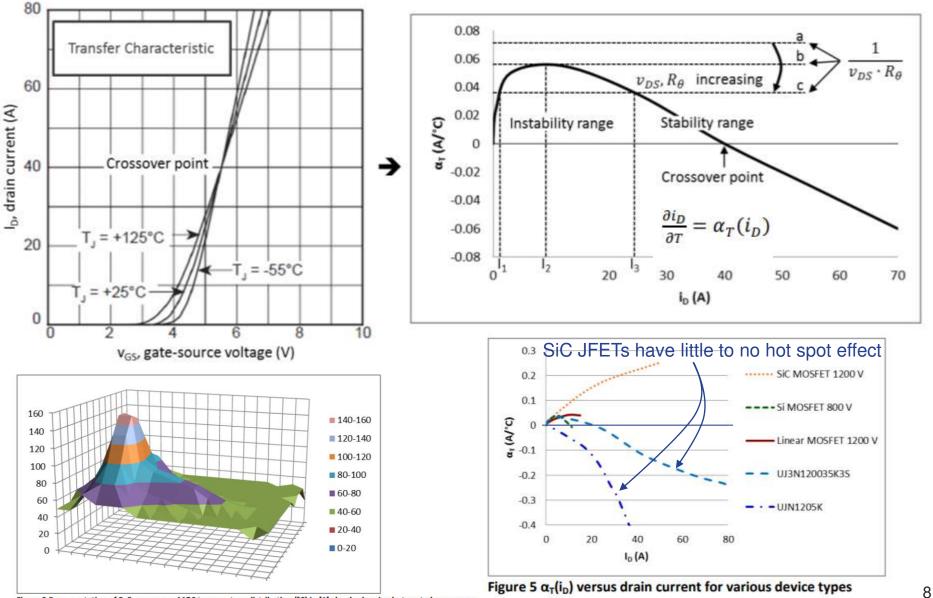

Figure 6 Typical transfer characteristics at V<sub>DS</sub> = 5V

Unlike SiC or Si MOSFETs, JFETs can be held stably in active mode, since the  $V_{GS}$  needed to sustain a given current increases with temperature, even down to relatively low currents

### **MOSFET Hot Spot in Active Mode**

Figure 2 Representation of 5x5 mm power MOS temperature distribution (°C) in [1] clearly showing hot spot phenomenon

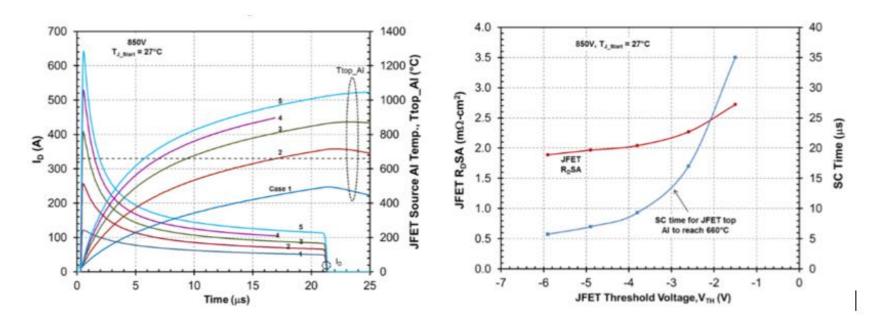

## SiC JFET/Cascode Short Circuit

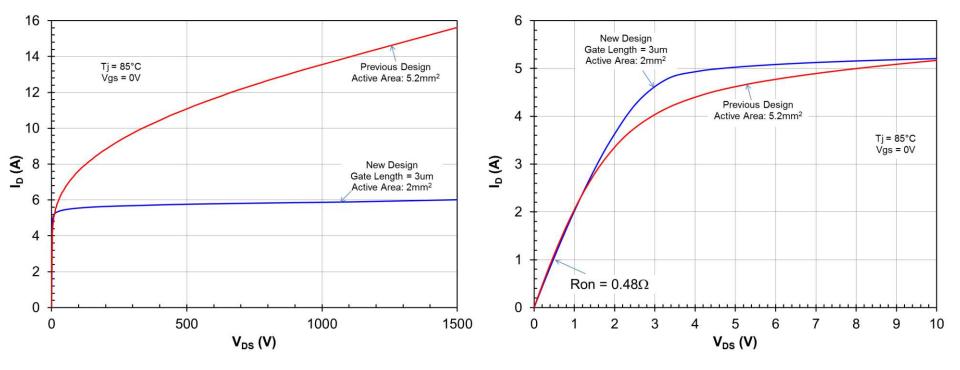

• RdsA tradeoff for trench SiC JFETs (UJC1206K)

SYSTEMS CENTER

• Peak saturation current can be decreased with little Rdson penalty

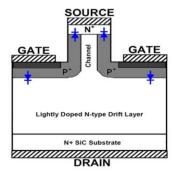

Figure 1: Cell structure of <u>SiC</u> trench JFET.

SYSTEMS CENTER

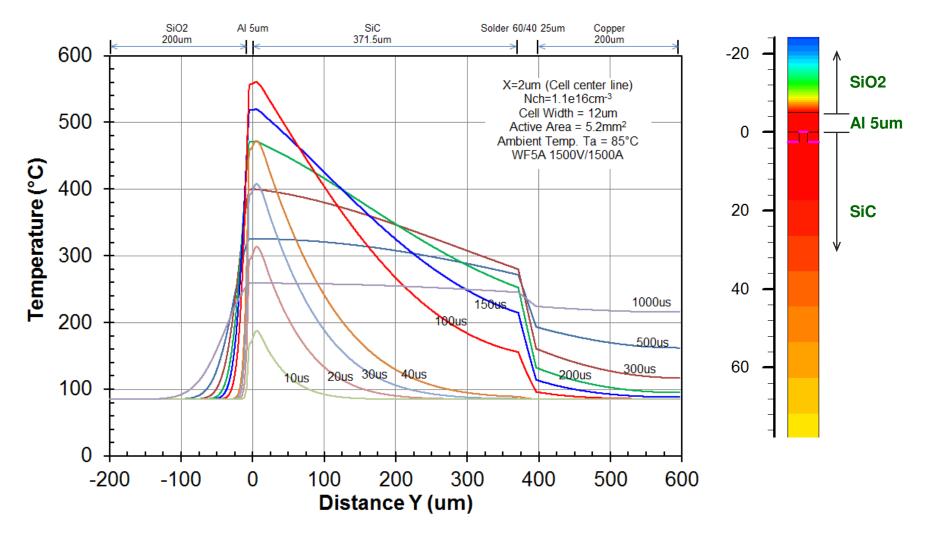

## FREE Setup for Electrothermal Simulations

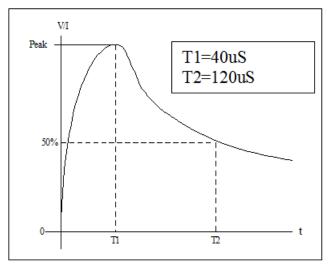

Surge waveform WF5A Vpeak (open circuit voltage) = 1500VSource impedance =  $1 \Omega$

Figure 2 Example Surge Waveform (WF5A)

| Layer<br>(From top to<br>bottom) | Thickness<br>um | Thermal<br>Conductivity<br>W/(K cm) | Heat Capacity<br>J/(K cm <sup>3</sup> ) |  |  |

|----------------------------------|-----------------|-------------------------------------|-----------------------------------------|--|--|

| SiO2<br>(Pkg mold)               | 200             | 0.014                               | 1.67                                    |  |  |

| Aluminum                         | 5               | 2.38                                | 2.33                                    |  |  |

| SiC                              | 371.5           | 4.55                                | 1.63                                    |  |  |

| Solder                           | 25              | 0.36                                | 1.57                                    |  |  |

| Copper (baseplate)               | 200             | 3.85                                | 3.42                                    |  |  |

SiO2 200um to model compound thermal insulating region

| Top Al 5um                               |

|------------------------------------------|

| SiC Surface region<br>– detail not shown |

| SiC 371.5um                              |

| Solder 25um                              |

| Cu 200um                                 |

|                                          |

UnitedSiC confidential

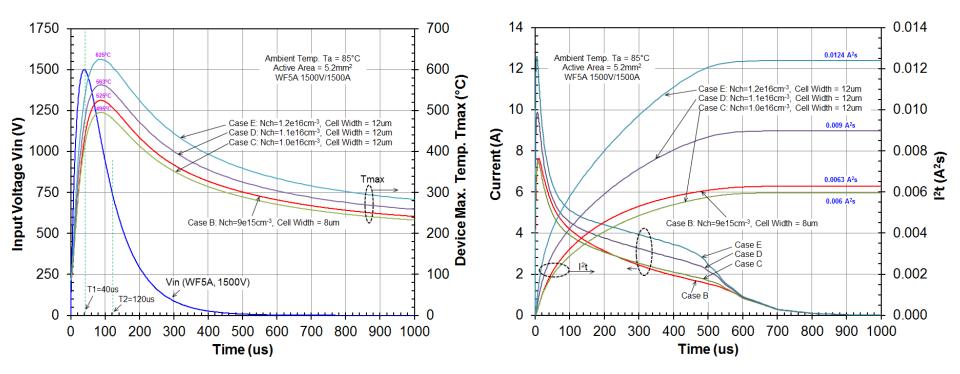

## Transient Thermal Simulations WF5A 1500V/1500A

|                       | Design | Ron<br>(Ω) | lsat @8<br>@10V | 35°C (A)<br>@1.5kV | Tmax<br>(°C) | lmax<br>(A) | l²t<br>(A²s) |            |

|-----------------------|--------|------------|-----------------|--------------------|--------------|-------------|--------------|------------|

| Recommended<br>Design | Case B | 0.58       | 2.5             | 12.3               | 525          | 7.6         | 0.0063       | 8um pitch  |

| Design                | Case C | 0.56       | 3.2             | 11.5               | 495          | 7.5         | 0.0060       |            |

|                       | Case D | 0.45       | 5.2             | 15.6               | 563          | 9.8         | 0.0090       | 12um pitch |

|                       | Case E | 0.39       | 7.4             | 19.9               | 625          | 12.6        | 0.0124       |            |

#### Temperature Distribution along Device Vertical Center Line for Design Case D

#### **Improved Current limiter DC Characteristics at 85°C** SYSTEMS CENTER

F

Avoid DIBL type effects for better saturation

### Inrush and Overvoltage Protection

SYSTEMS CENTER

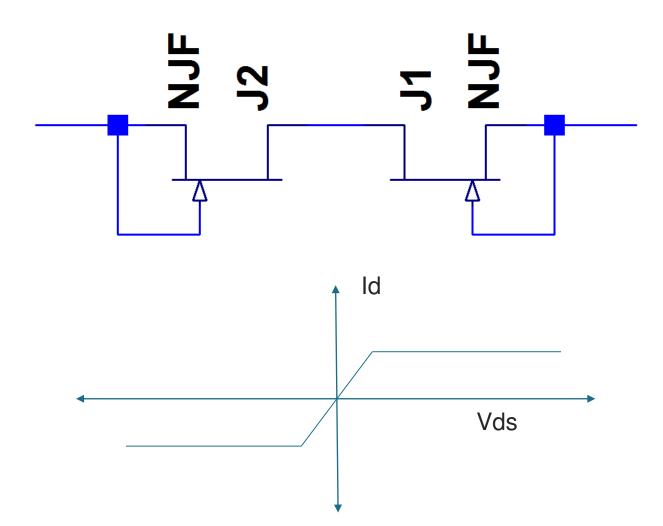

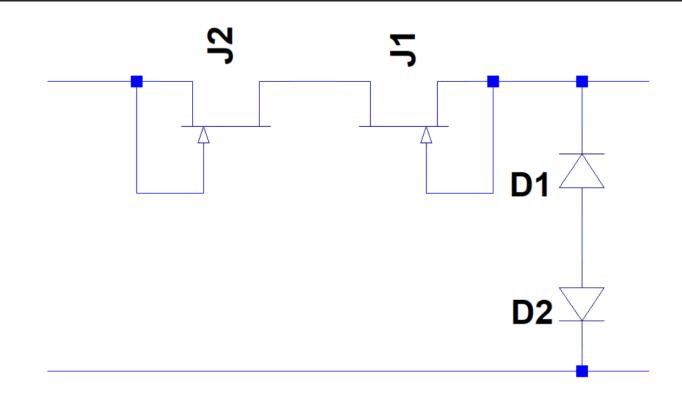

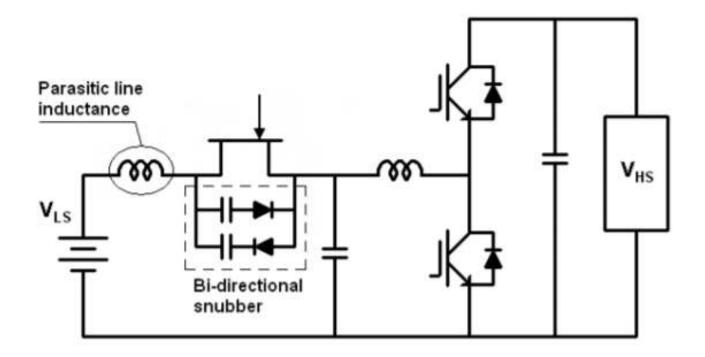

Common-drain JFETs – bidirectional inrush current limiting

D1,D2 – TVS diodes. Use Si at low voltages, SiC at high voltage

A MOV may be used across the SD if the line inductance energy becomes too high.

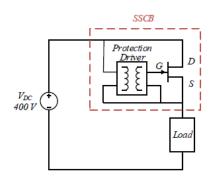

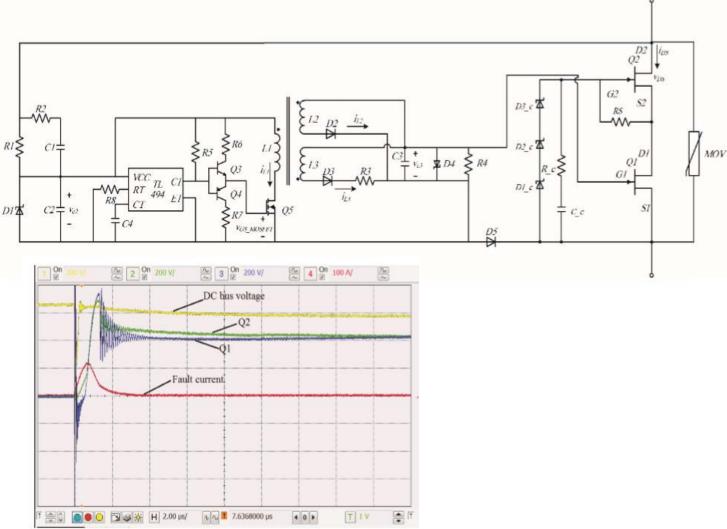

Fig. 1. A unidirectional self-powered SSCB using a normally-on SiC JFET as the main static switch and a fast-starting isolated DC/DC converter as the protection driver.

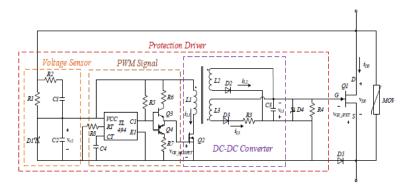

Fig. 2. A detailed circuit schematic of the SSCB with a combined forward-flyback DC/DC converter design.

Courtesy of the Illinois Institute of Technology

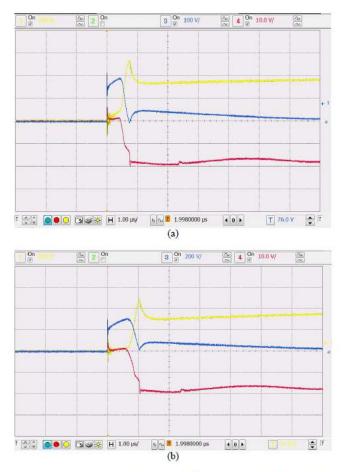

Fig. 9. Short circuit switching waveforms of SSCB with a combined forward-flyback protection driver with (a) 1  $\Omega$ , and (b) 2  $\Omega$  short circuit loop resistance. Time scale: 1 µs/division. BLUE is the JFET drain current  $i_{DS}$  waveform (100A/division). YELLOW is the JFET drain-source voltage  $v_{DS}$  waveform (200V/division). RED is the SiC JFET gate voltage  $v_{GS,JFET}$  waveform (10V/division). The response time is about 0.8 µs and 1 µs for (a) and (b) respectively.

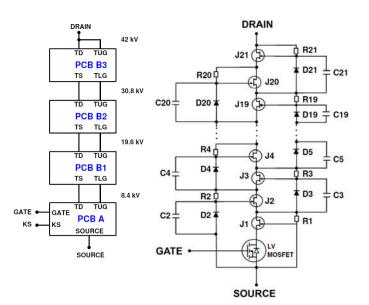

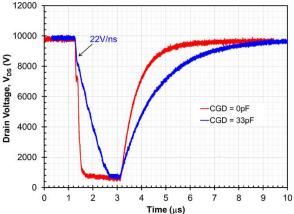

## Multi-Stage JFET Based Breaker

Fig. 7. Measured  $V_{DS}$  switching waveforms of Q1 (blue) and Q2 (green) during a short circuit fault. Time scale: 2  $\mu$ s/division.

F

SYSTEMS CENTER

Courtesy of the Illinois Institute of Technology

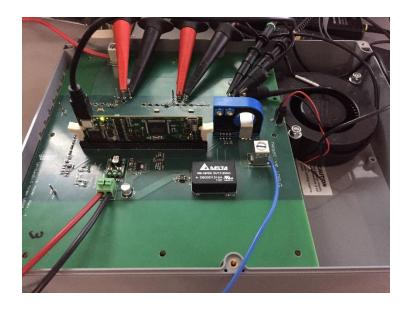

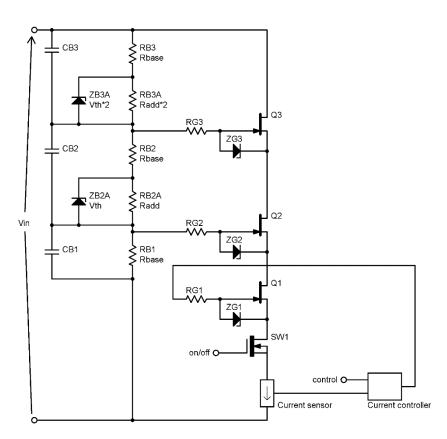

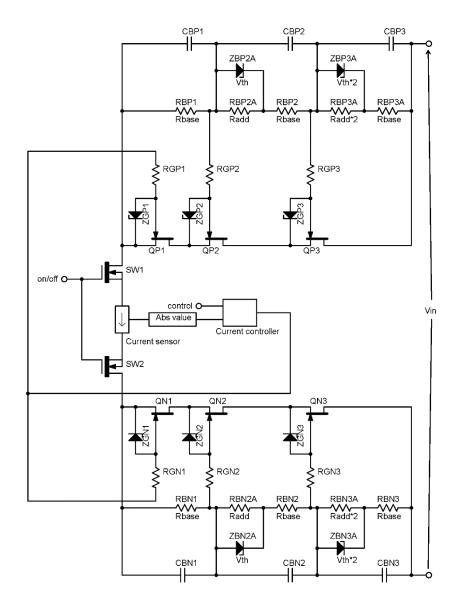

## **Controlled Current DC SSCB**

- Voltages automatically balanced

- Current controlled at any operating voltage

- Soft start

SYSTEMS CENTER

- Capacitor precharge

- Fault ride-through current limiter

- High voltage capability with fast turn-off feature

- Even if not operating at high voltage...

- Multiple JFETs dissipating power

- One current controller

- Lower cost than paralleling

## **Controlled Current AC SSCB**

AC current controlled with alternating voltage applied

CENTER

SYSTEMS

- Clean AC motor start

- Fault ride-through current limiter

- Bidirectional blocking, fast turnoff feature

- JFETs in reverse conduction are biased fully on because JFET is on when  $v_{GS} - v_{DS} > V_{GS(th)}$ . When  $v_{DS}$ is negative, JFET turns on more with increasing magnitude of its  $v_{DS}$  (caused for example by increased current through it), thus creating a positive reinforcement of turning on.

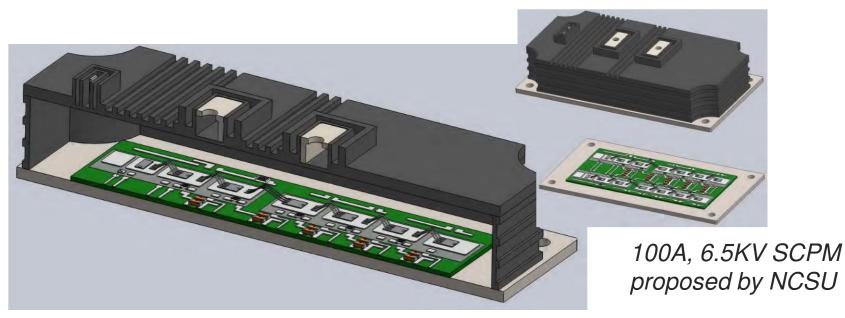

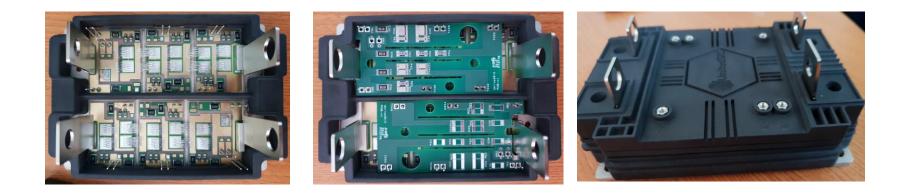

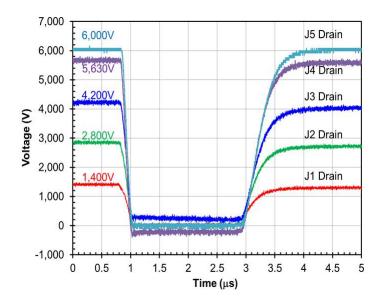

### **FREEDM HV Supercascodes**

#### 15KV, 40A built with discrete 45m, 1200v JFETs NCSU

## FREE High Voltage Applications

- 200A, 6500V half-bridge

- Solid state transformers, MV-XFC fast chargers, wind, traction, HVDC

- Uses a 5.7m, 1700V SiC JFET

- Can be utilized for HV DC breakers

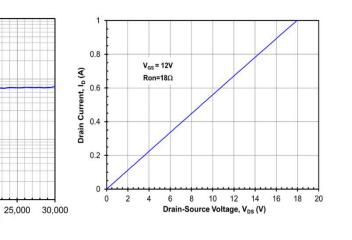

## **Ultra High Voltage Switches**

1A, 40KV Demo

SYSTEMS CENTER

1.E-03

1.E-04

1.E-05

1.E-06

0

5,000

10,000

15,000 20,000

Drain-Source Voltage, V<sub>DS</sub> (V)

Drain Current, I<sub>D</sub> (A)

Questions

### Anup Bhalla V.P. Engineering abhalla@unitedsic.com

| Property                                                                | Si   | GaAs | 6H-SiC    | 4H-SiC | GaN  | Diamond |

|-------------------------------------------------------------------------|------|------|-----------|--------|------|---------|

| Bandgap, Eg (eV)                                                        | 1.12 | 1.43 | 3.03      | 3.26   | 3.45 | 5.45    |

| Dielectric constant, $\varepsilon_r^{I}$                                | 11.9 | 13.1 | 9.66      | 10.1   | 9    | 5.5     |

| Electric Breakdown Field, E <sub>c</sub><br>(kV/cm)                     | 300  | 400  | 2500      | 2200   | 2000 | 10000   |

| Electron Mobility, $\mu_n$<br>(cm <sup>2</sup> /V·s)                    | 1500 | 8500 | 500<br>80 | 1000   | 1250 | 2200    |

| Hole Mobility, $\mu_p (\mathrm{cm}^2/\mathrm{V}\cdot\mathrm{s})$        | 600  | 400  | 101       | 115    | 850  | 850     |

| Thermal Conductivity, $\lambda$<br>(W/cm·K)                             | 1.5  | 0.46 | 4.9       | 4.9    | 1.3  | 22      |

| Saturated Electron Drift<br>Velocity, $v_{sat}$ (×10 <sup>7</sup> cm/s) | 1    | 1    | 2         | 2      | 2.2  | 2.7     |

#### Table I: Physical characteristics of Si and main wide bandgap semiconductors [1-3].

<sup>1</sup> $\varepsilon = \varepsilon_r \cdot \varepsilon_o$  where  $\varepsilon_o = 8.85 \times 10^{-12} \text{ F/m}$